Graphic LCD Contoller

|

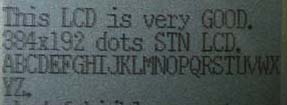

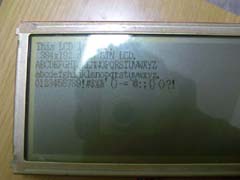

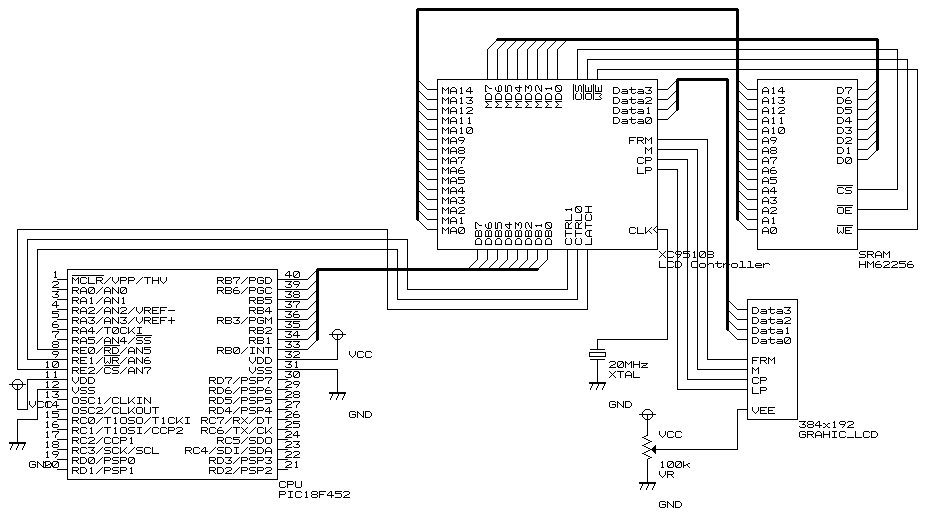

廐梩尨偺楅彜偱丄384x192僪僢僩丄儌僲僋儘俽俿俶塼徎偑\1,200偱攧傜傟偰偄傑偟偨丅 384x192偲偄偆偙偲偼丄8x16僪僢僩偺僼僅儞僩側傜丄48暥帤x12峴偺昞帵偑壜擻偱丄20暥帤4峴偺僉儍儔僋僞塼徎偺幚偵俈攞嫮偺忣曬検偑偁傝傑偡丅偦傟偑\1200側偺偱偡偐傜丄偲偰傕偍攦偄摼偩偲巚偄傑偡丅 偟偐偟丄偙偺塼徎偼僪儔僀僶俬俠偼幚憰偝傟偰偄傞傕偺偺丄廐寧偺QVGA僇儔乕塼徎偺傛偆偵VRAM傪撪憼偟偰偍傜偢丄忢偵昤夋偟偮偯偗側偗傟偽夋柺傪曐帩偡傞偙偲偑偱偒傑偣傫丅 傑偨丄嵟掅偱傕30fps偔傜偄偺僼儗乕儉儗乕僩偱昤夋偟側偄偲夋柺偑偪傜偮偄偰偟傑偄傑偟偨丅 侾僋儘僢僋偵係僪僢僩暘偺僨乕僞傪揮憲偡傞偱丄30fps偱昤夋偡傞偵偼384x192x30/4=553kHz偱僪僢僩僋儘僢僋傪憲傞偙偲偑昁梫偵側傝傑偡丅 侾廃婜偺娫偵丄RAM偐傜僨乕僞傪庢偭偰偒偰4bit偺僨乕僞傪弌椡偟丄僋儘僢僋僷儖僗憲弌丄96僋儘僢僋偛偲偵儔僀儞僷儖僗(Hsync憡摉)傪憲怣偟丄192儔僀儞偛偲偵僼儗乕儉僷儖僗(Vsync憡摉)傪憲怣偟側偔偰偼側傝傑偣傫丅 SH2儅僀僐儞偔傜偄側傜偱偒傞偱偟傚偆偑丄H8傗PIC偱惂屼偡傞偵偼偪傚偭偲張棟偑廳偡偓傑偡偟丄儅僀僐儞偵偼昞帵偡傞夋憸偺張棟傗丄僼僅儞僩偺揥奐側偳丄懠偵傕傗傞偙偲偑戲嶳偁傞偺偱丄愱梡偺俴俠俢僐儞僩儘乕儔偑梸偟偄偲偙傠偱偡丅丅 偦偙偱丄CPLD+SRAM傪梡偄偰丄LCD僐儞僩儘乕儔傪嶌惉偟丄昤夋偼偙偄偮偵擟偣偭偒傝偵偡傞偙偲偱丄旕椡側PIC偐傜偱傕偙偺塼徎傪僐儞僩儘乕儖偱偒傞傛偆偵偟傑偟偨丅 仜挿強丗CPU偼LCD偺昤夋張棟偐傜奐曻偝傟傞丅 仜抁強丗CPLD偺儅僋儘僙儖晄懌偵傛傝丄CPU僀儞僞乕僼僃僀僗偲SRAM傾僋僙僗夞楬偑旕摨婜丅 丂丂丂偙傟偵傛傝丄CPU偲CPLD偺僋儘僢僋傪撈棫偵偡傞偲丄SRAM偺僙僢僩傾僢僾僞僀儉偑 丂丂丂帪乆枮偨偣偢丄僑儈偑昞帵偝傟傞偙偲偑偁傞丅 丂丂丂仺CPU偲CPLD偵摨偠僋儘僢僋傪嫙媼偡傞偙偲偵傛偭偰偛傑偐偟偰偄傞 |

| 幨恀僐乕僫乕 | ||

| 僐儞僩儘乕儔婎斅 | CPU偼PIC傪巊梡 | |

|

|

|

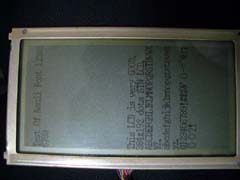

| 昞帵偝偣偰傒偨強 | 廲挿昞帵傕壜擻 | |

|

|

|

| 夞楬恾 | ||

| ||

| 娭楢僼傽僀儖 | ||

|

丒婎斅僷僞乕儞 丒CPLD僜乕僗 | ||